随着通信技术的发展,信号传输速率大幅度提高,工业应用和消费者的需求都对通信技术提出了更高的要求。在超高速数据传输应用中,串行通信技术逐渐成为了数据通信的主要方式。时钟数据恢复电路(Clock and Data Recovery,CDR)是接收系统中的核心模块,决定了接收器的性能,对整个串行通信系统十分重要。在信号传输过程中,传输介质、环境噪音以及信号本身的码间干扰等因素,都会使信号发生畸变。时钟数据恢复电路从畸变的数据信号中恢复出时钟信号,并利用时钟信号对数据进行再定时。

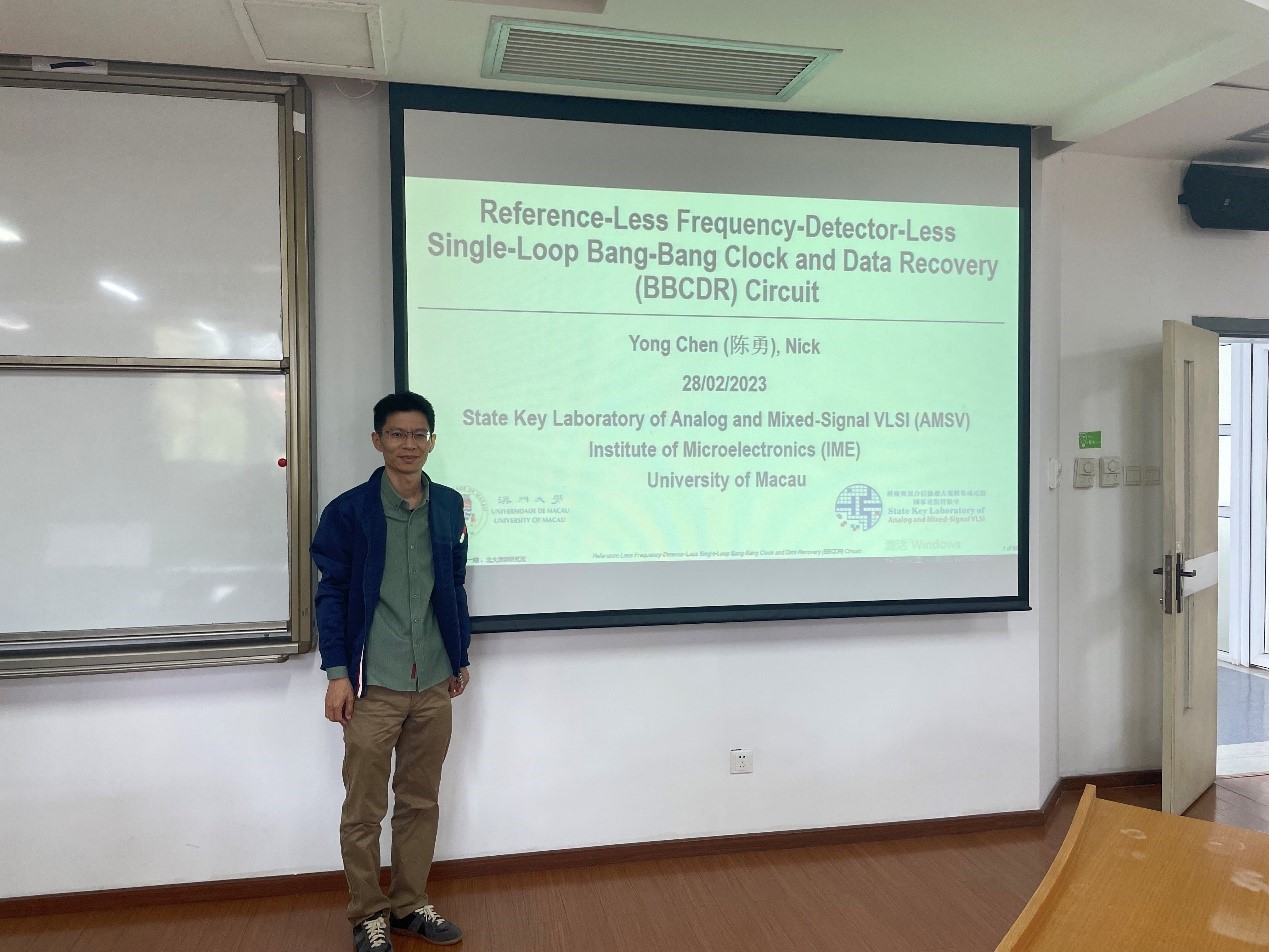

2月28日,我院邀请了澳门大学模拟与混合信号超大规模集成电路国家重点实验室的陈勇教授,分享了题为“Reference-Less Frequency-Detector-Less Single-Loop Bang-Bang Clock and Data Recovery (BBCDR) Circuit”的学术讲座。陈勇教授致力于集成电路领域的复合型和专业型领军和技术人才的培养,一直专注集成电路设计研究,涉及模拟/混合信号/射频/毫米波/有线通信等领域展开前沿的科学技术探索和研究。在芯片设计领域的主要国际期刊及国际会议发表学术论文近100 篇,授权中国专利18项。在本次讲座上,陈勇教授介绍了射频领域内的一些最前沿的关键技术,适用于未来高速无线通信和有线通信,并深入浅出地讨论他对于创新思维和人才培养的看法。

陈勇教授讲座现场

时钟和数据恢复(CDR)电路是高速有线接收机的核心电路,决定着其功率效率和吞吐量。在高密度数据中心中,电力和制冷成本分别高达总预算的25%和50%。因此,无需外部参考时钟源的CDR电路因其低成本、宽范围和低功耗而受到广泛关注。在讲座中陈勇教授介绍了他的团队所提出的CDR新方案,在传统全速率的bang-bang鉴相器(BBPD)中,连续三点采样的中间点采样时钟(CKS)与其余两采样时钟相位相反,其鉴相特性曲线关于原点对称,频率捕获能力有限。所提出的方案有意地为CKS引入偏移量(Strobe Point),从而获得单向的频率捕获能力。结合所提出的算法,所提出的CDR,在具有频差时,可自动搜索进入正确的频带,最终回归于正常锁定。该方案采用紧凑、低功耗的正交时钟方案以优化能量效率;无需数据采样时钟,因此适用于PAM-4信号制式;同时以单环的架构规避了双环路的环路切换引起的稳定性问题。

除了前沿领域外,陈勇教授也讨论了关于培养科研思维的重要性,鼓励学生的开放性思维和辩证的分析方法,给同学们带来很大的启发。

学院师生在听完讲座后颇有感触:

2021级 微电子硕士生 雷秦:

陈勇老师的讲解十分详细,对待科研的细致程度也很高,在科研的方法论上有独特的见解,也对我之后的科研学习有着参考价值。

2021级 微电子硕士生 付宇哲:

陈勇老师的讲座深入浅出,讲述了很多前沿的模拟电路工作,同时陈老师也分享了他的科研的思路,让我受益匪浅。

2021级 微电子博士生 周长春:

从陈老师多段截然不同的学习/研究经历总结出,改变现状(比如,换个环境和方向)能锻炼出新的思维方式。从特意放大波形不完美的地方来解决不完美的问题中,总结出,特意放大科学问题有时可以提供解决问题的新奇思路。

2021级 微电子硕士生 梁璨:

听完陈勇老师的讲座后,我对VCO的前沿发展有了新的认识,给予LC结构的VCO相比thyristor结构的VCO有着能效、振荡频率上的优势。并且,陈老师在科研方法上,用不完美来实现完美的思路,也让我深有启发。

陈勇教授介绍:

2005年毕业于中国传媒大学(原北京广播学院)广播电视工程专业;2010年在中国科学院微电子研究所获得博士学位;2010年进入清华大学微电子研究所做博士后研究;2013年起在新加坡南洋理工大学VIRTUS做Research Fellow;2016年加入澳门大学的模拟与混合信号超大规模集成电路国家重点实验室,现任长聘副教授。

OA系统

OA系统

学院邮箱

学院邮箱

教务管理

教务管理

资源下载

资源下载

English

English

发布时间:2023-03-10

发布时间:2023-03-10 浏览次数:

浏览次数: